LCMXO2-2000HC-4BG256C FPGA – Sistèm Ranje Pòtay Pwogramasyon sou Plas 2112 LUT 207 IO 3.3V 4 Vitès

♠ Deskripsyon pwodwi a

| Atribi pwodwi | Valè Atribi |

| Manifakti: | Treyi |

| Kategori pwodwi: | FPGA - Sistèm Pwogramasyon Pòtay sou Tèren |

| RoHS: | Detay |

| Seri: | LCMXO2 |

| Kantite Eleman Lojik: | 2112 LE |

| Kantite Antre/Sòti: | 206 Antre/Sòti |

| Vòltaj Alimantasyon - Min: | 2.375 V |

| Vòltaj Alimantasyon - Maksimòm: | 3.6 V |

| Tanperati Minimòm pou Fonksyònman: | 0 C |

| Tanperati maksimòm pou opere: | + 85 C |

| To Done: | - |

| Kantite Transceiver: | - |

| Stil montaj: | SMD/SMT |

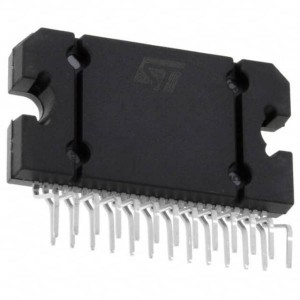

| Pakè / Ka: | CABGA-256 |

| Anbalaj: | Plato |

| Mak: | Treyi |

| RAM distribye: | 16 kbit |

| RAM blòk entegre - EBR: | 74 kbit |

| Frekans Operasyon Maksimòm: | 269 MHz |

| Sansib a imidite: | Wi |

| Kantite Blòk Tablo Lojik - LAB: | 264 LABORATWA |

| Kouran ekipman pou fonksyònman: | 4.8 mA |

| Vòltaj Alimantasyon Operasyonèl: | 2.5 V/3.3 V |

| Kalite pwodwi: | FPGA - Sistèm Pwogramasyon Pòtay sou Tèren |

| Kantite pake faktori: | 119 |

| Sou-kategori: | Sikwi Lojik Pwogramasyon |

| Memwa Total: | 170 kbit |

| Non komèsyal: | MachXO2 |

| Pwa inite: | 0.429319 ons |

1. Achitekti Lojik Fleksib

• Sis aparèy ak 256 a 6864 LUT4 ak 18 a 334 I/O Aparèy ki konsome anpil mwens enèji

• Pwosesis avanse 65 nm ki ba pouvwa

• Jis 22 µW pouvwa an sibstiti

• Antre/Sòti diferansyèl ba pwogramab

• Mòd sibstiti ak lòt opsyon ekonomize enèji 2. Memwa entegre ak distribye

• Jiska 240 kbits sysMEM™ RAM blòk entegre

• Jiska 54 kbit RAM distribye

• Lojik kontwòl FIFO dedye

3. Memwa Flash Itilizatè Sou Chip la

• Jiska 256 kbit memwa flash itilizatè

• 100,000 sik ekriti

• Aksesib atravè koòdone WISHBONE, SPI, I2 C ak JTAG

• Ka itilize kòm yon PROM processeur mou oswa kòm yon memwa Flash

4. Antre/Sòti senkronize sous pre-fabrike

• Rejis DDR nan selil I/O yo

• Lojik angrenaj dedye

• Angrenaj 7:1 pou Antre/Sòti Ekspozisyon

• DDR jenerik, DDRX2, DDRX4

• Memwa DDR/DDR2/LPDDR dedye ak sipò DQS

5. Segondè pèfòmans, memwa tanpon I/O fleksib

• Tanpwen sistèm sysIO™ pwogramab la sipòte yon pakèt interfaces:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, MLVDS, RSDS, LVPECL

– SSTL 25/18

– HSTL 18

– Antre deklanchman Schmitt, jiska 0.5 V isterèz

• Antre/Sòti sipòte socket cho

• Tèminasyon diferansyèl sou chip la

• Mòd rale-anwo oswa rale-anba pwogramasyon

6. Fleksibilite sou chip revèy

• Uit revèy prensipal

• Jiska de revèy kwen pou koòdone I/O gwo vitès (sèlman sou bò anwo ak anba)

• Jiska de PLL analòg pou chak aparèy ak sentèz frekans fraksyonèl-n

– Gwo ranje frekans antre (7 MHz rive 400 MHz)

7. Ki pa volatil, rekonfigurab san limit

• Limen imedyatman

– li limen nan mikwosegond

• Solisyon an sekirite ak yon sèl chip

• Pwogramasyon atravè JTAG, SPI oswa I2C

• Sipòte pwogramasyon background nan ki pa volatil

8. memwa mozayik

• Demaraj doub opsyonèl ak memwa SPI ekstèn

9. Rekonfigirasyon TransFR™

• Mizajou lojik sou teren pandan sistèm nan ap fonksyone

10. Sipò Nivo Sistèm Amelyore

• Fonksyon ranfòse sou chip: SPI, I2C, revèy/kontè

• Osilateur entegre ak yon presizyon 5.5%

• TraceID inik pou swiv sistèm nan

• Mòd Pwogramasyon Yon Sèl Fwa (OTP)

• Yon sèl ekipman pou pouvwa ak yon ranje fonksyònman pwolonje

• Eskanè limit IEEE Standard 1149.1

• Pwogramasyon nan sistèm ki konfòm ak IEEE 1532

11. Gwo varyete opsyon pakè

• Opsyon pake TQFP, WLCSP, ucBGA, csBGA, caBGA, ftBGA, fpBGA, QFN

• Opsyon pake ki gen ti anprint

– Ti tankou 2.5 mm x 2.5 mm

• Migrasyon dansite sipòte

• Anbalaj avanse san alojèn